後段熱壓退火製程增強節點強度

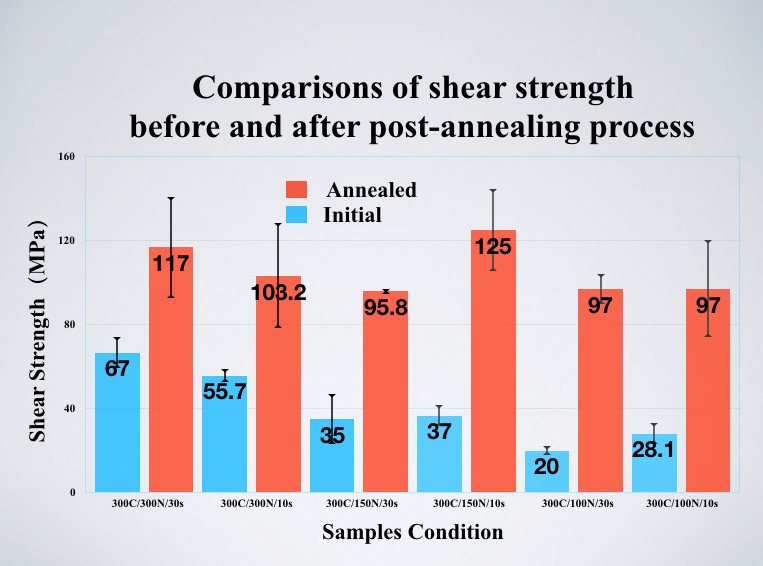

此篇主要探討在銅銅接合與高度<111>優選方向的奈米雙晶銅中,接合時間與溫度對於接合強度的關係。 我們在10秒和30秒內進行即時接合製程,並在300℃下進行一小時熱處理,再將試片在氬氣環境下進行二次退火研究接點強度之變化。為了與這組樣品進行比較,我們生產沒有第二階段退火處理的試片,既“快速接合”。 我們發現與沒有後後段退火的試片相比較,後段退火樣品的接合強度與其電性有顯著的提高。為了分析第二階段退火的正面效果,我們使用剪切試驗獲得定量結果以比較強度差異。 另外,我們也使用四點探針測量來測量電阻,發現帶有第二階段退火的樣品的電阻更低低且更穩定。

後段退火製程

接點強化

電子封裝

銅銅接合

熱壓接合

3DICs

Bonding

智慧半導體奈米系統技術研究中心

半導體微電子封裝

高抗拉強度奈米雙晶銅導線用於重新佈線層(RDLs)

奈米雙晶銅

Nanotwinned Cu

高韌性

高強度

重新佈線層

RDL

FOWLP

Fan-out

扇出型封裝

銅導線

奈米雙晶銅應用於低溫/快速銅-銅接合與高韌性銅導線

銅-銅直接接合技術所製作的銅微凸塊接點被預期是下一世代可以取代3D IC中的微凸塊焊錫接點。是近20年來科學上極富挑戰的議題。因(111)面為最密堆積平面,其平面上的銅原子擴散速度較快的特性,團隊發展低溫低壓的銅銅接合技術,目前已可成功在一般真空環境(10^-3 torr)下,以低溫(150°C)低壓(~1MPa)進行銅-銅接合,接合過程可在60分鐘內完成,也能在300°C、78 MPa下5秒接合完成。可應用於CMOS影像感測元件及高頻寬記憶體的接合,兩者都需要超高I/O數以及低熱預算(Low thermal budget). 這方面的成果目前是世界領先研究群之一。 另外,<111>奈米雙晶銅也能應用於高強度、高延性扇出(Fan-out)封裝細線路重佈線層 (RDL)扇出型封裝(fan-out package)係在IC封裝時,將晶片先切割獨立後,再用樹脂重新組合成一個新的晶圓,再以晶圓的形式進行redistribution layer (RDL)佈線,如附圖一。Cu RDL 重分布層為實現 ”Fan-Out ”之必要結構。其中細線化(FineLine RDL)技術的實現,將能滿足手持式行動裝置的需求。下世代的扇出型封裝計畫將數個不同的晶片,在樹脂晶圓重組的時候就放在一起,而利用fine line RDL在不同晶片間互聯。由於RDL這時候會橫跨矽晶片和樹脂,個別的熱膨脹係數(Coefficient of thermal expansion)各不相同,使得Cu RDL受到拉扯及壓縮,造成斷線。這種失效模式在RDL線寬小於5um開始發生,於是業界需要高強度且高熱穩定性的電鍍銅。由於雙晶本身具有阻擋差排(dislocation)移動的功能,其強度可達一般電鍍銅的2至3倍。而且有很好的熱穩定性。

可調控奈米雙晶銅之機械性質應用於鋰電池集電板

奈米雙晶銅

鋰電池集電板

Nanotwinned Cu

高強度

高延展性

高電遷移壽命奈米雙晶銅用於重新佈線層RDLs

奈米雙晶銅

電遷移

重新佈線層

RDL

FOWLP

Fan-out

nanotwinned Cu

扇出型封裝

銅導線

奈米雙晶銅

Nanotwinned Cu

高韌性

高強度

高抗電遷移

低溫/快速銅-銅接合

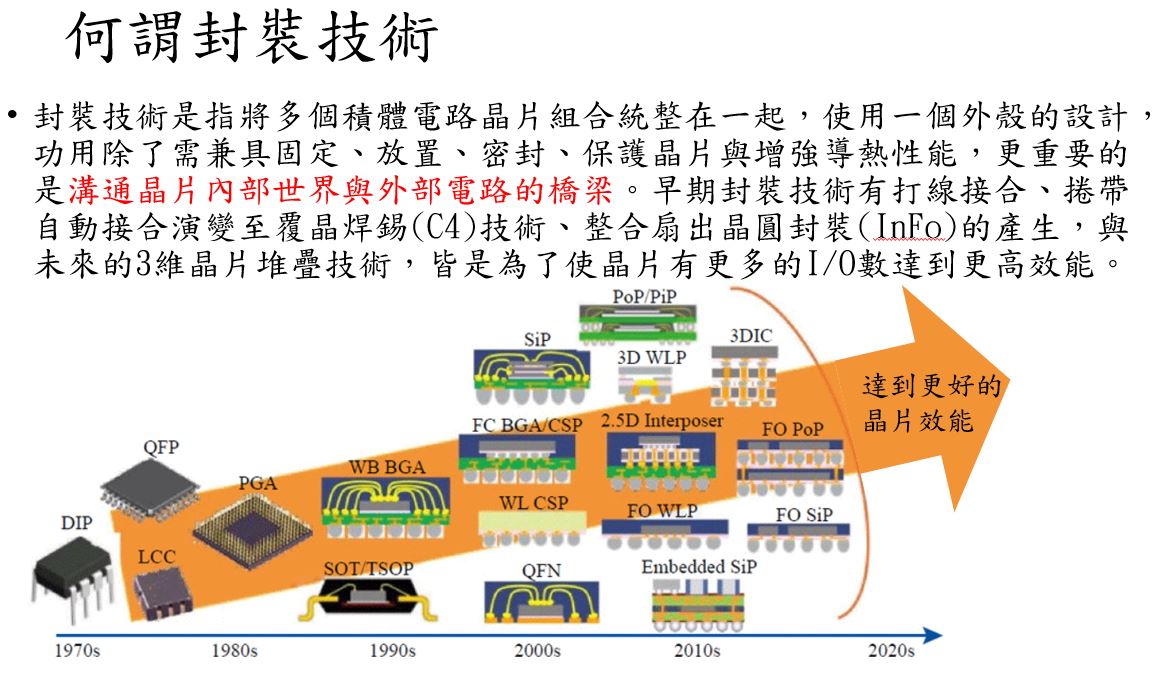

封裝技術簡介

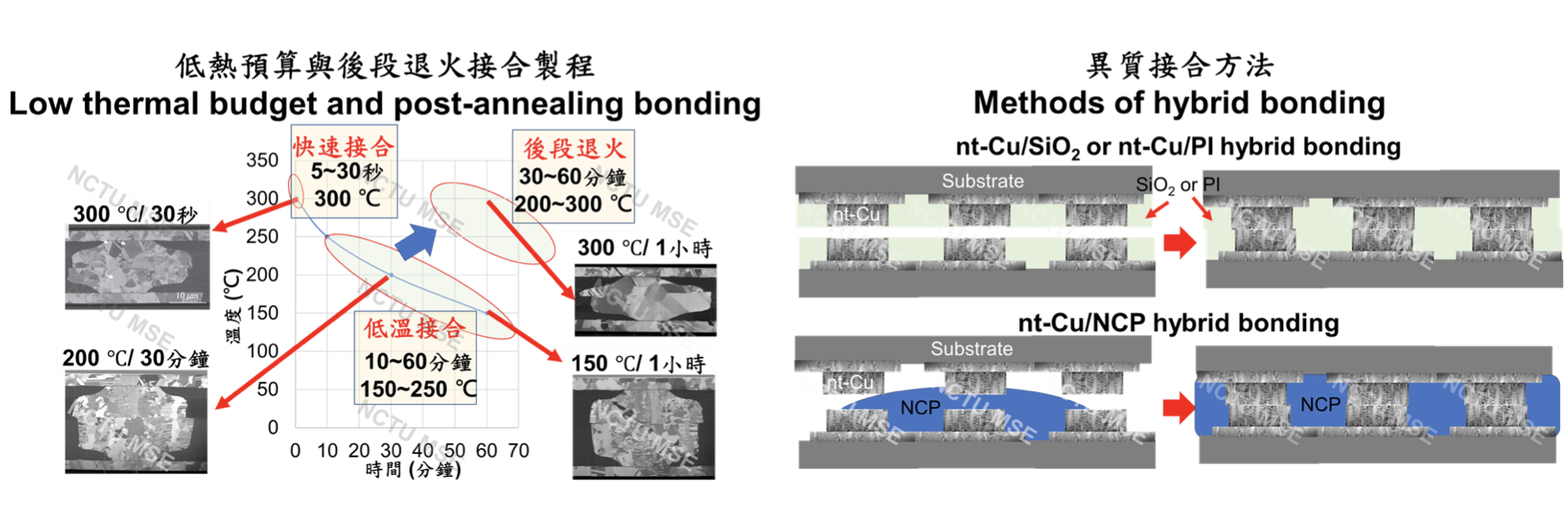

低熱預算銅銅接合(包含快速接合與低溫接合)

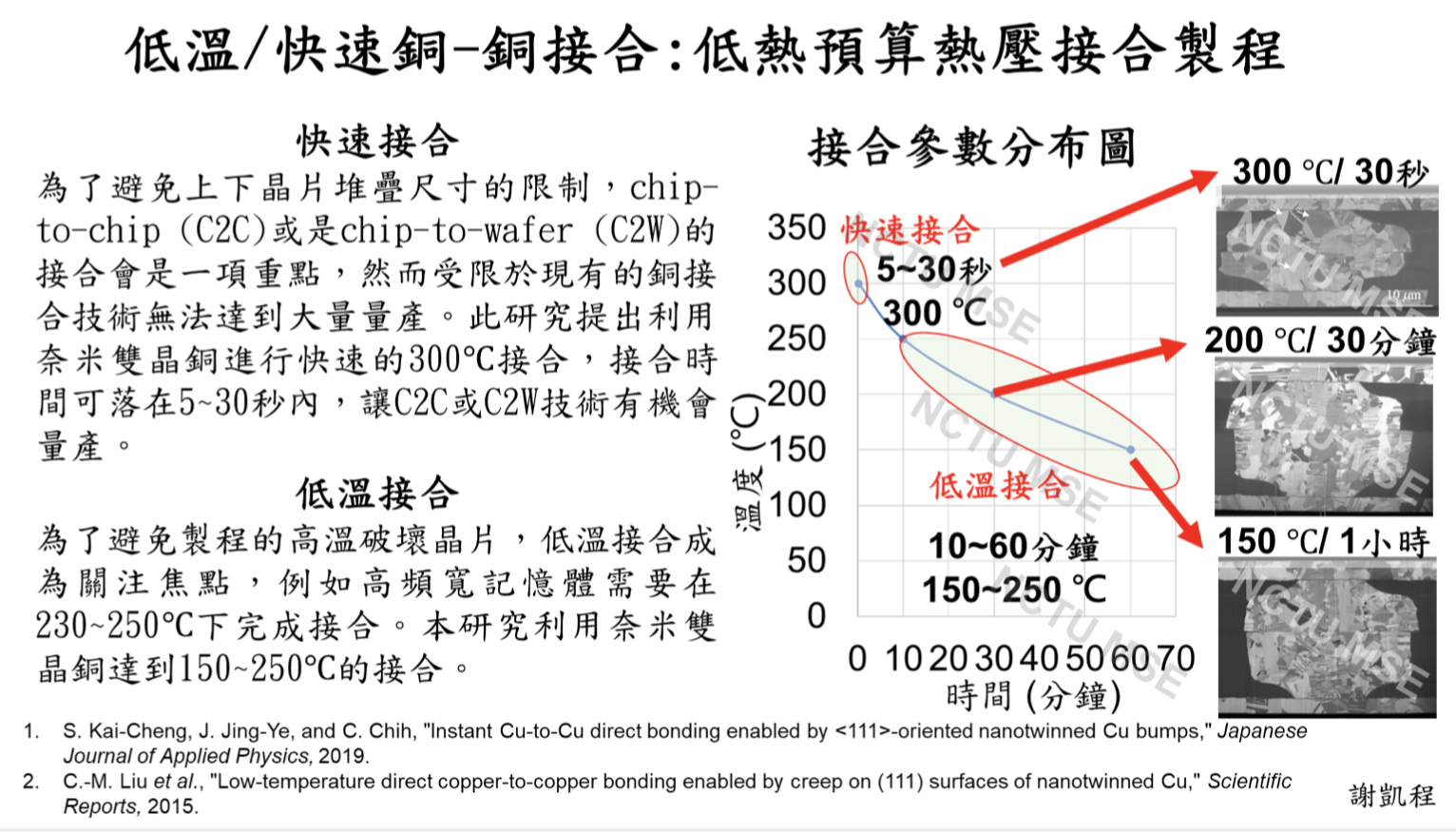

這部分將介紹低熱預算製程,或是low thermal budget process。 此議題在封裝領域一直是很重要的目標,因為熱與時間牽涉到原子的擴散程度,當溫度越高、原子擴散越快;當時間越長、原子擴散越遠,一旦原子濃度在整個晶片中偏離預想結果,將會造成晶片的功能異常。因此,降低熱預算的方法可從兩大方向著手: 第一個是減少加熱製程的時間、第二個則是降低加熱的溫度。本技術引入奈米雙晶銅的特殊性質,發展出快速接合與低溫接合兩個重要方向,達到這兩個降低熱預算的要求。 快速接合的溫度在300C,而時間可以壓縮到30s以內,甚至是5s,此接合製程除了降低熱預算,還能夠加速生產速率,有望在未來完成chip-to-wafer等製程的量產。 低溫接合的溫度則可以降低到250C以下,甚至降到150C,在記憶體等元件封裝上有重要的價值。

銅銅接合

電子封裝

bonding

低熱預算

快速接合

瞬時接合

低溫接合

智慧半導體奈米系統技術研究中心

半導體微電子封裝

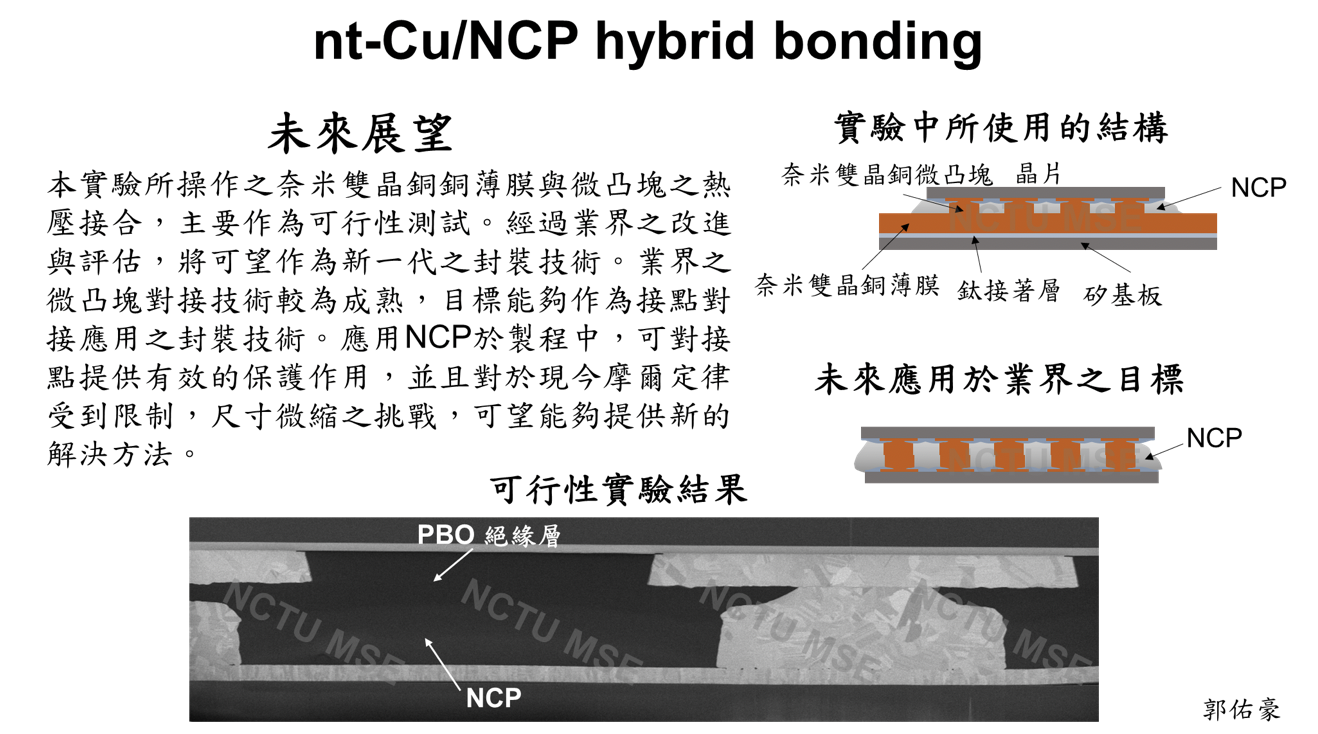

銅對非導電膠之異質接合

此篇替各位介紹使用非導電膠NCP於奈米雙晶銅薄膜進行異質接合的製程。 首先我們將試片放入超音波振洗機,進行振洗,接著分別利用丙酮、異丙醇與檸檬酸等藥品進行清潔,再使用去離子水沖洗乾淨,以確保試片表面的清潔度。 接著,在室溫下於奈米雙晶銅薄膜塗上非導電膠NCP,再蓋上鍍有微凸塊的晶片並施力,使得NCP能夠均勻填入凸塊間的縫隙中。 我們使用的接合夾具為這種三螺絲夾具,透過較大的接觸面積,使得施力能夠較為均勻,接著便放入爐管進行熱壓接合。 接合過程中,爐管是不會抽真空的,也因此我們能夠在大氣環境下進行接合,能夠同時完成Bonding以及NCP的Curing,達到不錯的良率,接合強度佳,NCP的填充性也不錯,在業界中具有應用潛力。 希望未來透過業界之改進與評估,能夠成為新一代的封裝技術之一,將奈米雙晶銅應用於接點間的接合。在現今追求尺寸微縮的趨勢下,NCP能夠為接合提供良好保護,可望能夠成為一個不錯的解決方式。

Non-Conductive paste

hybrid bonding

電子封裝

3DICs

半導體微電子封裝

智慧半導體奈米系統技術研究中心

異質接合

2020_ECTC完整版

(111)奈米雙晶銅應用於銅-銅接合與異質接合

銅銅接合

奈米雙晶銅

Copper nano-twin

3DICs

異質接合

未來科技展媒合網址

電鍍<111>奈米雙晶銅,能提升銅接點的電與機械性質,成為下一世代的銅接點的重要材料。能夠應用在三種領域1. 低熱預算/低電阻銅對銅直接接合我們能在300℃時大約5秒的時間後立即完成接合,同時達到低的接觸電阻。五秒能完成銅-銅接合,目前是文獻最快的世界紀錄2. 高韌性銅導線 3. 鋰電池銅箔

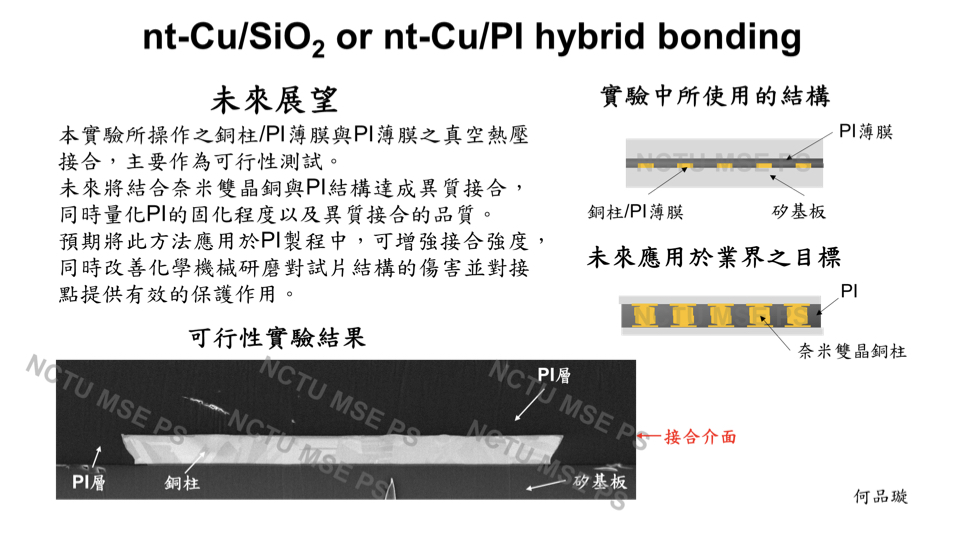

銅對聚亞醯胺之異質接合

本篇介紹聚亞醯胺 (Polyimide, PI)和銅的異質接合製程。 首先,試片結構分為含有銅柱和PI薄膜的結構,以及單純PI薄膜的結構。將其中高分子升溫固化至相同程度,此固化程度(Degree of imidization)能夠同時保有繼續交聯的性質和一定的機械強度,因此能夠相容化學機械研磨的製程。 經過化學機械研磨(CMP)後,完成初步的試片,能夠露出銅柱以及PI的表面。 接著再使用檸檬酸清潔,最後以去離子水沖洗乾淨。所有製程過程與銅-銅接合製程相容。 接著使用螺絲夾具對銅柱/PI薄膜對接PI薄膜施力,並且放入爐管中進行真空熱壓接合。 透過上述製程,能夠調控PI薄膜和銅的結構,使其具有穩定的機械性質,並且仍然能夠繼續完成固化以及接合,在微電子封裝產業中具有應用潛力。 本製程所操作之銅柱/PI薄膜對接PI薄膜之真空熱壓接合,主要作為可行性測試。 未來將結合奈米雙晶銅材料與PI結構達成異質接合,同時能夠量化PI的固化程度(Degree of imidization)以及異質接合的品質。 未來希望能夠將此方法應用於封裝製程中,不但能夠增強接合強度並且改善化學機械研磨對試片結構造成的傷害,同時對接點提供有效的保護作用。

3DICs

新穎材料

Polyimide

聚亞醯胺

Hybrid bonding

電子封裝

智慧半導體奈米系統技術研究中心

半導體微電子封裝

異質接合

2020_ECTC完整版

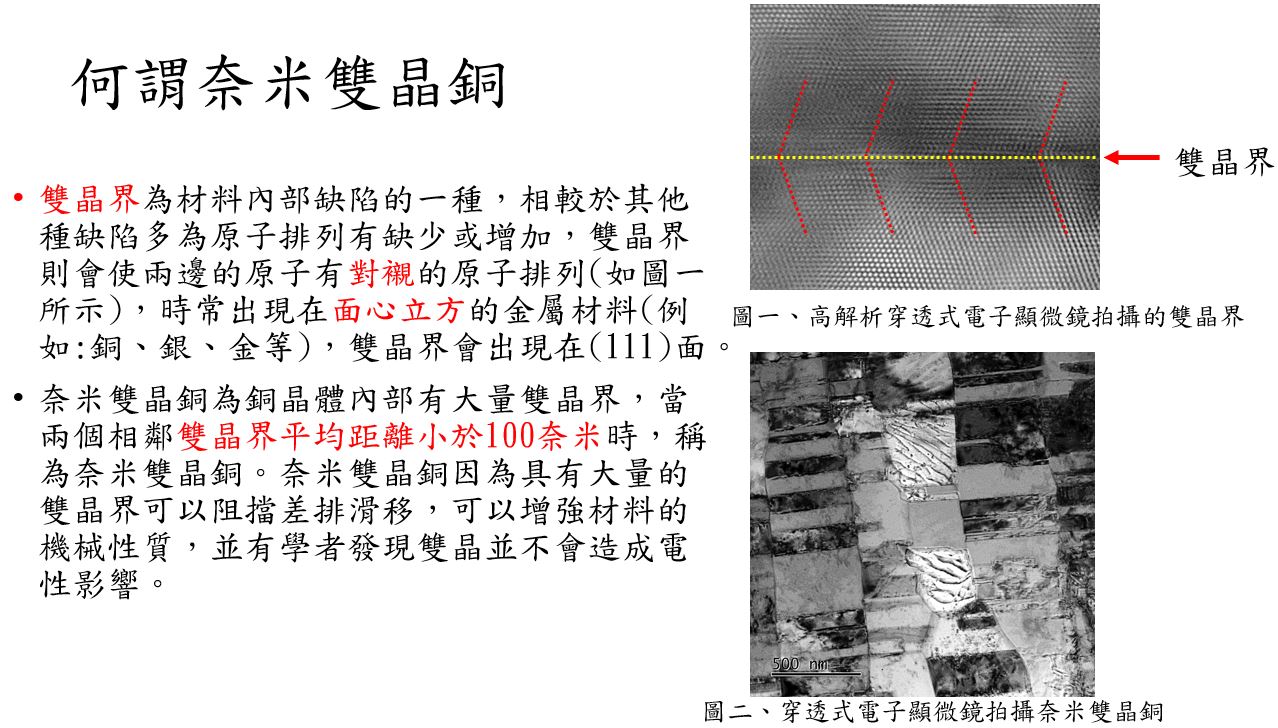

奈米雙晶銅簡介